2022年3月,intel、amd、arm、高通、三星、台积电、ase、google cloud、meta和微软十家巨头成立chiplet标准联盟,制定了通用chiplet的高速互联标准ucie(universal chiplet interconnect express)。同年,作为测试测量领域优质的供应商keysight宣布加入ucie联盟。

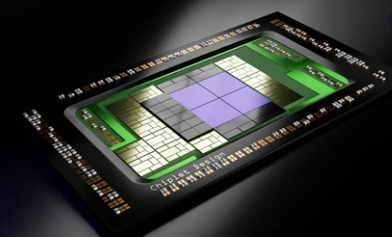

后摩尔时代的拯救者chiplet

在过去数十年,半导体制程及工艺基本支持着摩尔定律在不断推进,在性能不断增强,晶体管的尺寸不断微缩,制程工艺的节点逐渐来到3nm 2nm接近极限制程,随之带来的则是跳跃式的设计和制作成本增长。那么伴随着摩尔定律逐渐放缓,我们来到了后摩尔时代,行业瞩目的chiplet(小芯片/芯粒)技术像是带来了曙光,成为了持续提高soc高集成度和算力密度的重要途径,下面我们就来简要介绍一下该技术。

形象的讲chiplet其实是一种积木游戏,通过2.5d/3d集成封装等技术,能够将不同工艺节点、不同功能、不同材质的芯片,如同搭积木一样集成一个更大的系统级芯片(soc)。追本溯源,其实chiplet并不是一项新技术,早在十年前就被提出,像近期采用了ultrafusion封装架构的m1 ultra芯片就是chiplet的成功应用,通过两颗m1 max晶粒的内部互连,提供了高于市面16核pc 90%运算性能。随后由几家巨头主导的mcm(multi-chip module)cowos(chip-on-wafer-on-substrate)emib(embedded multi-die interconnect bridge)等底层先进的封装成为主流,为chiplet的推广提供了极大的助力。

问:那么chiplet优点在哪里呢?

答:1.通过把大芯片分割成面积较小的芯片,可有效改善生产的良率,降低晶圆制造成本。

2.可根据不同ip的需求,将不需要最先进制程的元件独立出来,使用制程成熟的元件替换,从而进一步降低制造成本。

3.通过在芯片设计阶段将soc按功能分解成一个个芯粒,从而重复利用部分模块化芯粒,达到降低设计难度和设计成本。

ucie助力新兴技术chiplet

新兴技术chiplet如果要成为主流的技术,就需要统一多家供应商的各种功能芯片的各类设计、互连、接口标准,标准化chiplets之间交互的通信互连协议。2022年3月由多家国际半导体巨头联合推出了ucie 1.0 spec,该标准针对chiplet技术建立,致力于推动芯片互联的标准化发展,构建出相互兼容的芯片生态系统。下面我们就来简单看一下ucie规范相关内容。

ucie 1.0支持不同的数据传输速率,位宽,凸点间隔,还有通道,来保证最广泛的可行的互用性。ucie中定义了一个边带接口使设计和验证变得容易。其中互联的单簇的组成单元是包含了n条单端、单向、全双工的数据线(标准封装n=16,高级封装n=64),一条单端的数据线用作有效信号,一条线用于追踪,每个方向都有一个差分的发送时钟,还有每个方向的两条线用于边带信号(单端,一条是800mhz的时钟,一条是数据线)。高级封装中支持把空闲的线束作为错误处理线束(包括时钟,有效信号,边带信号等),标准封装选项中支持位宽退化来处理错误。多簇的ucie互联可以组合起来在每条连接链路上提供更优的性能。

ucie 是一种分层协议,它包含物理层(含封装)、d2d适配层和协议层。物理层负责处理电信号、时钟信号、链路训练和边带信号等。d2d适配层则为chiplet提供链路状态管理和参数调整。通过使用循环冗余校验crc和链路级重传机制保证数据的可靠传输。此外,d2d适配层配备了底层仲裁机制用于支持多种协议,以及通过数据宽度为256字节的流量控制单元(flit)进行数据传输的底层传输机制。

如今,pcie和cxl协议已经被广泛部署在几乎所有的板级计算单元上,因此ucie通过在协议层本地端提供pcie和cxl协议映射,以利用现有的生态和资源来确保各互连设备之间的无缝交互。借助pcie和cxl,可以将已部署成功的soc构建、链路管理和安全凯发国际娱乐平台的解决方案直接迁移到ucie。ucie还定义了一种“流协议”,可用于映射其他协议。

在ucie 1.0定义了如下两种类型的封装,其中标准封装(2d)成本效益更高,而更先进的封装(2.5d)则是为了追求更高的功率。在实际的设计中,由多种商用的封装方式可供选择。ucie规范支持这些类别中所有类型的封装选择。

ucie的测试挑战

ucie标准化的统一架构将会大大促进chiplet开放生态的发展,这意味着生态链中的不同环节ip、芯片设计、封装设计、设计服务等需要统一和可靠的标准实现互连,各个芯粒部件和系统整合所需要严格的互操作测试标准,目前ucie 1.0标准初步定义了一致性和调试的初期框架,规范组织也在规划相应的认证体系架构,如下图所示,在基础规范之上,ucie联盟的工作组将会制定专门的测试规范,包括从物理层、适配层、协议层、对各个子部件进行互操作和一致性测试,通过标准化一致性测试流程和方法,保证芯片的可靠整合。

可以预期ucie将面临众多测试挑战,从测试可行性上需要考虑被测部件与golden部件的互操作测试,bist测试,环回测试,及各芯片子部件自身的电气及协议一致性测试,从测试方法学上,面临诸如可测试性设计等问题,对于芯片封装级整合后,是否需要进行信号探测,目前我们也看到一些芯片公司会在芯片验证阶段设计集成封装治具,或者使用探针台进行精密尺寸互联表征和信号参数表征测试,此外ucie也定义了跨封装的结构,通过光引擎或者电retimer实现机柜级的互连,这种场景更接近于传统光或电测试方法。相信在不远的将来,ucie联盟的成员和测试工作组会针对这些问题进行梳理和讨论,将会完成统一的测试标准和流程。

目前来说,keysight是业内唯一完整提供从设计仿真、物理层、电气到协议层验证的供应商,为ucie的设计仿真到互连和信号测试方案提供坚实基础。下图为是德科技针对pcie 6.0和cxl完整的凯发国际娱乐平台的解决方案。

keysight pcie 6.0和cxl测试凯发国际娱乐平台的解决方案一览

先进的封装和半导体制造技术将会在未来的10年在计算界掀起新的革命。ucie已经蓄势待发,keysight将会结合本身丰富的测试测量经验,助力ucie产业联盟测试测量相关规范。

- 浏览量:760

- 来 源:是德科技

- 编辑:仪器仪表wxf

- 声明:凡本网注明" 来源:仪商网"的所有作品,凯发国际娱乐平台的版权均属于仪商网,未经本网授权不得转载、摘编使用。

经本网授权使用,并注明"来源:仪商网"。违反上述声明者,本网将追究其相关法律责任。

本网转载并注明自其它来源的作品,归原凯发国际娱乐平台的版权所有人所有。目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。如有作品的内容、凯发国际娱乐平台的版权以及其它问题的,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

本网转载自其它媒体或授权刊载,如有作品内容、凯发国际娱乐平台的版权以及其它问题的,请联系凯发国际娱乐平台。相关合作、投稿、转载授权等事宜,请联系本网。

qq:2268148259、3050252122。 -

-

是德科技扩展再生电力系统凯发国际娱乐平台的解决方案以支持电动汽车和可再生能源系统企业动态|2024-10-18

是德科技扩展再生电力系统凯发国际娱乐平台的解决方案以支持电动汽车和可再生能源系统企业动态|2024-10-18 -

恭喜fluke 9500c高性能示波器校准器荣获“cec 2024年度最佳产品奖”企业动态|2024-10-16

恭喜fluke 9500c高性能示波器校准器荣获“cec 2024年度最佳产品奖”企业动态|2024-10-16 -

中国移动携手信而泰首次发布国产400g全栈仪器仪表及测试套件,共推算力网络高质量发展企业动态|2024-10-16

中国移动携手信而泰首次发布国产400g全栈仪器仪表及测试套件,共推算力网络高质量发展企业动态|2024-10-16 -

安立公司增强wlan测试仪支持wi-fi 7 2x2 mimo企业动态|2024-10-16

安立公司增强wlan测试仪支持wi-fi 7 2x2 mimo企业动态|2024-10-16 -

深化合作,携手共赢,禾赛科技获零跑汽车下一代车型平台激光雷达独家定点企业动态|2024-10-16

深化合作,携手共赢,禾赛科技获零跑汽车下一代车型平台激光雷达独家定点企业动态|2024-10-16 -

签约全球战略合作,均胜电子助力广汽埃安加速布局全球市场企业动态|2024-10-16

签约全球战略合作,均胜电子助力广汽埃安加速布局全球市场企业动态|2024-10-16 -

艾普斯电源 x 慕尼黑电子展 2024:展示升级电力测试凯发国际娱乐平台的解决方案企业动态|2024-10-15

艾普斯电源 x 慕尼黑电子展 2024:展示升级电力测试凯发国际娱乐平台的解决方案企业动态|2024-10-15 -

同惠电子荣获首届“未来20 · 2024中国a股上市公司成长力年度企业”称号企业动态|2024-10-15

同惠电子荣获首届“未来20 · 2024中国a股上市公司成长力年度企业”称号企业动态|2024-10-15 -

北方微电子院推出新产品高精度mems智能传感器企业动态|2024-10-14

北方微电子院推出新产品高精度mems智能传感器企业动态|2024-10-14 -

上海微系统所“超灵敏快速检测芯片式热分析仪”项目荣获全国颠覆性技术创新大赛卓越奖企业动态|2024-10-14

上海微系统所“超灵敏快速检测芯片式热分析仪”项目荣获全国颠覆性技术创新大赛卓越奖企业动态|2024-10-14